そういえば、PIC24Fのデジタル入力ポートにも、プルアップ抵抗(50k)が内蔵されているのでした。この内部のプルアップ抵抗のおかげでデジタルI/O入力が解放状態でもHighレベル状態を保ちますが・・

でも、初期状態のままでは、内蔵プルアップ抵抗は無効なのです。CNPUnで目的の端子のプルアップを有効にすれば使えます。リセット状態では、無効になります。

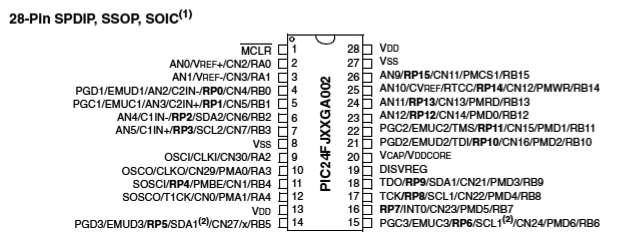

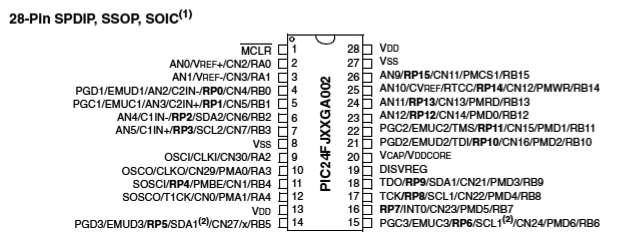

なお、PIC24FJ の内部プルアップのビット位置は、そのポート番号とは何ら関係がない位置です。チップのピン番号に対する機能割り付け一覧表の、CN番号がCNPUn用のビット番号になります。

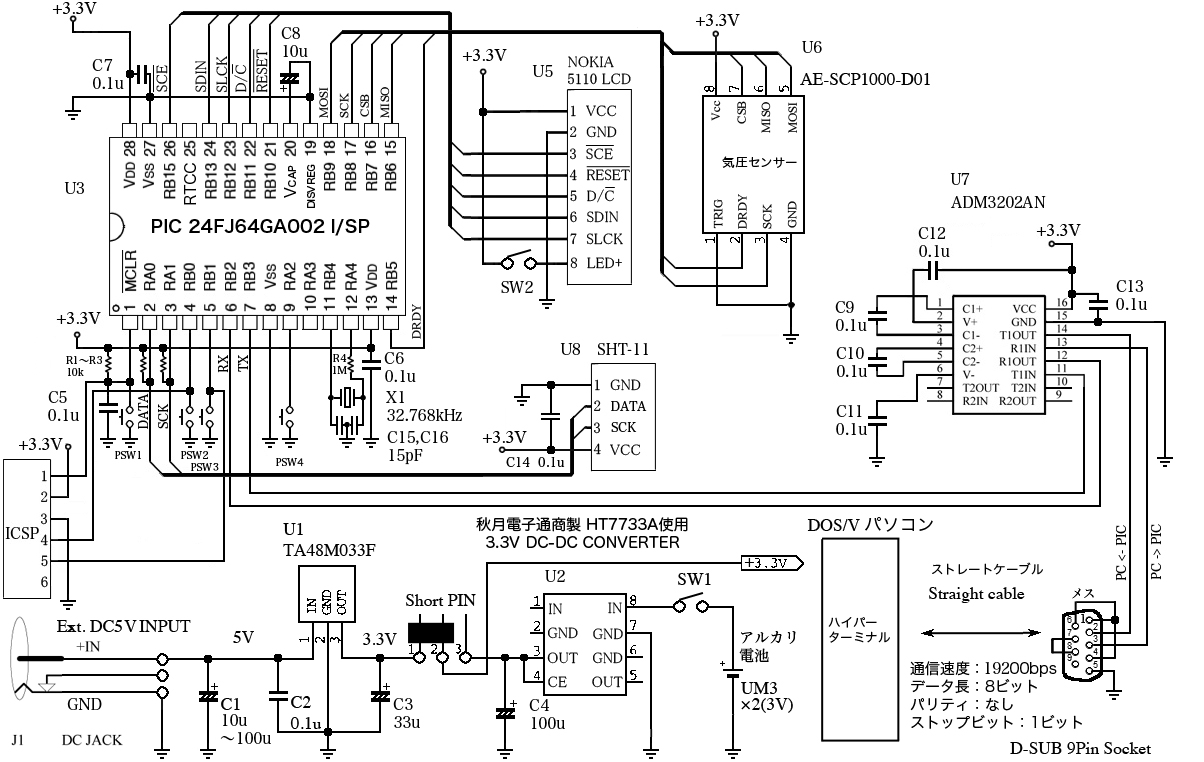

今回は、RB0(CN4)、RB1(CN5)、RA2(CN30)に押しボタンスイッチがあるので、

CNPU1 = 0x0030

CNPU2 = 0x4000

となります。

今回の回路では、ICSP接続でプログラミング中に、共用している押しボタンさえ押さなければ、ICSPとRB0、RB1(PIC24FJのPGECx/PGEDx端子)を、押しボタンスイッチ入力と共有できます。

なぜならば、リセット状態でICSP接続通信を行いプログラミングしますので、リセットが解除されて、プログラムが走ってプルアップの再設定がされるまでは、プルアップが無効なのです。これはICSP接続の端子にも都合がいいのです。

ディップスイッチ等の、フリー状態で開放にならないスイッチと共有すると、いちいちICSP動作時にディップスイッチをOPENにしなければなりません。

これを忘れると、ICSP出力がグランドとショートします。でも、押しボタンなら押さなければ必ずスイッチとしてはOPEN状態ですから安心ですが・・

押しボタンを押しながらICSPで書き込んだらアウトですが、少なくとも私はそんな面倒な事はしません。

よーし、これでハード回路がやっと定まった。

そして、システム全体の処理も移植しなくては・・

今度こそ、例によっていつになる事やら!趣味ですから・・(Oct. 18th 2010)

|